## **ADE-31 LOGIC BOSS**

2 stage, Switched, Cascading, Logic Module

## **USER GUIDE**

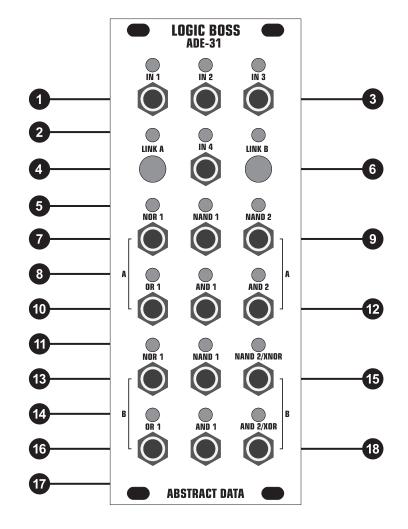

## 1: Front

Page 2 of 3

## 2: Technical

Page 3 of 3

| OVERVIEW:    | 2 stage, switched, cascading, logic module<br>Up to 4 inputs & 12 outputs – simultaneously<br>Unlinking gives 2 independent 6 part stages<br>Link stages by CV & on-board switching<br>RTL works on all input types – not just logic<br>LED indicators for all inputs & outputs<br>Power supply reverse-voltage protection<br>Low-profile build mounts in any depth rack |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

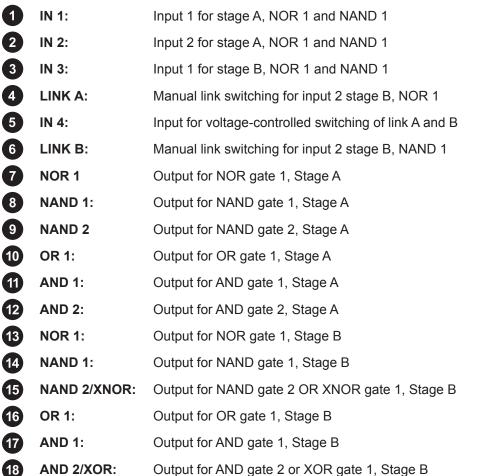

| STAGE A:     | 1: NOR 1:                                                                                                                                                                                                                                                                                                                                                                |

|              | 2x input (IN 1 / IN 2)<br>2: NAND 1:                                                                                                                                                                                                                                                                                                                                     |

|              | 2x input (IN 1 / IN 2)                                                                                                                                                                                                                                                                                                                                                   |

|              | 3: NAND 2:<br>2x input (OR 1[A] / NAND 1[A])                                                                                                                                                                                                                                                                                                                             |

|              | 4: OR 1:                                                                                                                                                                                                                                                                                                                                                                 |

|              | 1x input (NOT(NOR 1[A]))                                                                                                                                                                                                                                                                                                                                                 |

|              | 5: AND 1:                                                                                                                                                                                                                                                                                                                                                                |

|              | 1x input (NOT(NAND 1[A]))<br>6: AND 2:                                                                                                                                                                                                                                                                                                                                   |

|              | 1x input (NOT(NAND 2[A]))                                                                                                                                                                                                                                                                                                                                                |

| STAGE B:     | 7: NOR 1:<br>2x input (IN 3 / Link A state (AND2[A] or Low))                                                                                                                                                                                                                                                                                                             |

|              | <ul> <li>8: NAND 1:</li> <li>2x input (IN 3 / Link B state (AND2[A] or Low))</li> </ul>                                                                                                                                                                                                                                                                                  |

|              | 9: NAND 2 (Unlinked):<br>2x input (OR 1[B] / NAND 1[B])                                                                                                                                                                                                                                                                                                                  |

|              | XNOR (Linked):<br>3x input (OR 1[B] / NAND 1[B] / IN 3)                                                                                                                                                                                                                                                                                                                  |

|              | 10: OR 1:<br>1x input (NOT(NOR 1[B]))                                                                                                                                                                                                                                                                                                                                    |

|              | 11: AND 1:<br>1x input (NOT(NAND 1[B]))                                                                                                                                                                                                                                                                                                                                  |

|              | 12: AND 2: (Unlinked)<br>1x input (NOT(NAND 2[B]))                                                                                                                                                                                                                                                                                                                       |

|              | XOR: (Unlinked)<br>1x input (NOT(XNOR))                                                                                                                                                                                                                                                                                                                                  |

| PRECAUTIONS: | The ADE-31 uses the Doepfer standard for power connection and cable orientation. The RED stripe on the supplied power cable connects to the NEGATIVE (-12V) rail on the ADE-31 with the RED stripe facing DOWN. This is marked on the back of the ADE-31 PCB as "-12 RED".                                                                                               |

|              | The ADE-31 has diode and polyfuse protection built in but an incorrectly connected cable may still cause damage to the module or the power supply.                                                                                                                                                                                                                       |

|              | The rear panel of the ADE-31 has exposed parts and connections. Please<br>ensure when handling the ADE-31 that the unit is held by the sides of the<br>front panel or the sides of the PCB.                                                                                                                                                                              |

| CREDITS:     | Rory Dow<br>Dave White                                                                                                                                                                                                                                                                                                                                                   |